1.introduce

1.1 Features

| Subsystem | Features |

| Cortex®-A53 MPCore platform | Quad Cortex®-A53 processors operation up to 1.6 GHz |

| Support of 64-bit Arm® v8-A architecture | |

| 512 KB unified L2 cache | |

| Cortex®-M7 core platform | • Microcontroller available for customer application |

| Cortex®-M7 CPU operating up to 800 MHz | |

| Image Sensor Processor (ISP) | 375 Mpixel/s HDR ISP supporting configurations, such as 12MP@30fps, 4kp45, or |

| External memory interface | 32-bit DRAM interfaces: |

| 8-bit NAND-Flash, including support for Raw MLC/SLC devices, BCH ECC up to | |

| eMMC 5.1 Flash (2 interfaces: uSDHC1 and uSDHC3) | |

| SPI NOR Flash (3 interfaces) | |

| FlexSPI Flash with support for XIP (for Cortex®-M7 in low-power mode) and support | |

| On-chip memory | Boot ROM (256 KB) |

| On-chip RAM (868 KB): | |

| Graphic Processing Unit | • GC7000UL with OpenCL and Vulkan support • 2 shaders • 166 million triangles/sec • 1.0 giga pixel/sec • 16 GFLOPs 32-bit • Supports OpenGL ES 1.1, 2.0, 3.0, OpenCL 1.2, Vulkan • Core clock frequency of 1000 MHz • Shader clock frequency of 1000 MHz • GC520L for 2D acceleration • Render target compatibility between 3D and 2D GPU (super tile status buffer) |

| Video Processing Unit | Video Decode • 1080p60 HEVC/H.265 Main, Main 10 (up to level 5.1) • 1080p60 VP9 Profile 0, 2 • 1080p60 VP8 • 1080p60 AVC/H.264 Baseline, Main, High decoder Video Encode • 1080p60 AVC/H.264 encoder • 1080p60 HEVC/H.265 encoder |

| Neutral Processing Unit (NPU) | 2.3 TOP/s Neural Network performance • Keyword detect, noise reduction, beamforming • Speech recognition (i.e. Deep Speech 2) • Image recognition (i.e. ResNet-50) |

| HDMI 2.0a Tx | HDMI 2.0a Tx supporting one display • Resolutions of: 720 x 480p60, 1280 x 720p60, 1920 x 1080p60, 1920 x 1080p120,3840 x 2160p30 • Pixel clock up to 297 MHz Audio support • 32-channel audio output support • 1 SPDIF audio eARC input support |

| LCDIF Display Controller | Support up to 1920x1200p60 display per LCDIF if no more than 2 instances used simultaneously, or 2x 1080p60 + 1x 4kp30 on HDMI if all 3 instances used simultaneously .• One LCDIF drives MIPI DSI, up to UWHD and WUXGA • One LCDIF drives LVDS Tx, up to 1920x1080p60 • One LCDIF drives HDMI Tx, up to 4kp30 |

| Audio | • Cadence® Tensilica® HiFi 4 DSP, operating up to 800 MHz • SPDIF input and output, including a raw capture input mode • Six external synchronous audio interface (SAI) modules supporting I2S, AC97,TDM, codec/DSP, and DSD interfaces, comprising one SAI with 8 TX and 8 RXlanes, one SAI with 4 TX and 4 RX lanes, two SAI with 2 TX and 2 RX lanes, andtwo SAI with 1 TX and 1RX lane. • All ports support 49.152 MHz BCLK. • ASRC supports processing 32 audio channels, 4 context groups, 8 kHz to 384 kHzsample rate, and 1/16 to 8x sample rate conversion ratio. • eARC/ARC• 8-channel PDM mic inpu |

| MIPI Interface | Two instances of 4-lane MIPI CSI interface and HDR ISP • For single Camera, MIPI CSI 1 can support up to 400/500 MHz pixel clock in theNominal/Overdrive mode. • For single Camera, MIPI CSI 2 can support up to 277 MHz pixel clock. • For dual Camera, both MIPI CSI can support up to 266 MHz pixel clock. • 2x ISP supporting 375 Mpixel/s aggregate performance and up to 3-exposureHDR processing. •When one camera is used, support up to 12MP@30fps or 4kp45 •When two cameras are used, each supports up to 1080p80 4-lane MIPI DSI interface • Maximum resolution limited to resolutions achievable with a 250 MHz pixel clock and active pixel rate of 200 Mpixel/s with 24-bit RGB. This includes resolutions such as: •1080 p60•WUXGA (1920x1200) at 60 Hz •1920x1440 at 60 Hz •UWHD (2560x1080) at 60 Hz •MIPI DSI: WQHD (2560x1440) can be supported by reduced blanking mode |

| GPIO and pin multiplexing | General-purpose input/output (GPIO) modules with interrupt capability |

| Input/output multiplexing controller (IOMUXC) to provide centralized pad control | |

| Power management | Temperature sensor with programmable trip points |

| Flexible power domain partitioning with internal power switches to support efficient power management | |

| Connectivity | One PCIe Express (PCIe) Single Lane supporting PCIe Gen3 • Dual Mode operation to function as root complex or endpoint • Integrated PHY interface • Supports L1 low power sub-state |

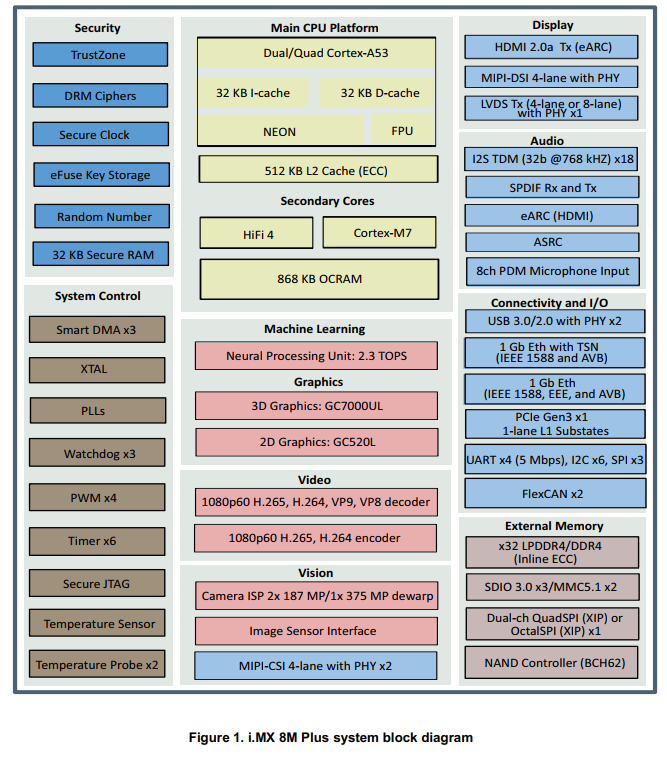

1.2 Block diagram

Fi gure 1 shows the functional modules in the i.MX 8M Plus processor system.

2.Build your repo

1.Fork https://github.com/boundarydevices/boundary-bsp-platform

2.modify " .repomanifestsdefault.xml" add and modify module.

3.Build code Compile server

3.1.ubuntu22.04TLS

32 sudo apt install openssh-server

3.3 sudo apt-get install samba

3.4 Build environment configuration "MACHINE=nitrogen8mp DISTRO=boundary-xwayland . setup-environment build"

3.5 Build image "MACHINE=nitrogen8mp bitbake boundary-image-multimedia-full"